Moku Cloud Compileを使用すると、Moku FPGA上に独自のデジタル信号処理(DSP)を簡単に実装できます。FPGAプログラミングは通常、ハードウェア記述言語(HDL)で行われます。HDLコーディングの習得はソフトウェアプログラミング言語に比べて難しい場合があります。そこでこのチュートリアルでは、MATLABとSimulinkを使用してDSPの動作/アルゴリズムをプログラミングおよび構築し、Mokuプラットフォームへの実装用のVHDLコードを自動生成する方法を説明します。このチュートリアルのパート1では、MATLABスクリプトをVHDLコードに変換する方法と、 第2部 チュートリアルのこの部分では、Simulink モデルを VHDL コードに変換する方法を説明します。

概要

Mokuクラウドコンパイル

Liquid InstrumentsのMoku Cloud Compile(MCC)ツールを使用すると、Mokuプラットフォームに実装するためのカスタム計測器を設計できます。CPUや特定用途向け集積回路(ASIC)ベースのDSPアプローチと比較して、FPGAはASICレベルの入出力レイテンシを実現しながら、CPUと同様にソフトウェア定義で再プログラム可能です。FPGAプログラミングは通常、ハードウェア記述言語(HDL)で行われます。HDLコーディングの習得はソフトウェアプログラミング言語に比べて難しい場合がありますが、他のプログラミング言語のスクリプトをHDLに変換できるツールがいくつかあります。このチュートリアルでは、MathWorks HDL Coderを使用してMATLABコードをHDLコードに変換し、Moku:Proに実装する方法を説明します。

このチュートリアルのパートIでは、MATLAB HDL Coderを使用したVHDLコード生成についてのみ説明します。この方法は、MATLABでのプログラミングに既に慣れているユーザーに推奨されます。 第2部 このチュートリアルでは、SimulinkモデルからVHDLコードを生成する方法について説明します。Simulinkモデルのブロックダイアグラム形式は、システムとデータフローの可視化を容易にし、ユーザーはMATLAB関数ブロックを設計に追加することもできます。より複雑なシステムの場合、両方のツールを活用することで、設計プロセスを大幅に効率化できます。

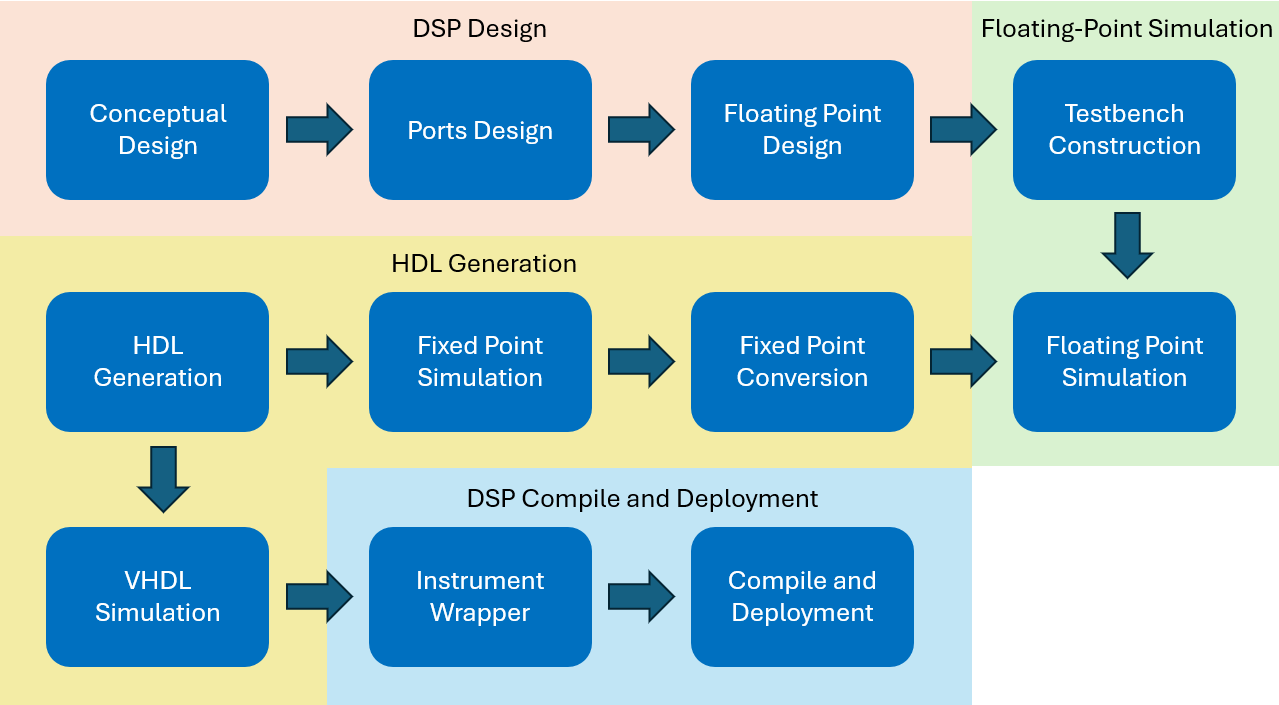

MATLAB HDL Coder メソッドの設計プロセスは、図 4 のように、DSP 設計、浮動小数点シミュレーション、HDL 生成、DSP の展開と検証の 1 つの最上位ステージに分類できます。以下の手順に従って、MATLAB HDL Coder を使用して Moku:Pro に実装するデジタル シュミット トリガーを構築します。

図 1: Cloud Compile + HDL Coder DSP 設計の推奨ワークフロー。

シュミットトリガー

シュミットトリガはコンパレータ回路の一種です。入力が特定の電圧閾値を超えているか下回っているかに基づいて、1ビットのデジタル出力を生成します。標準的なオペアンプベースのコンパレータは、閾値がXNUMXつしかありません。ノイズの多い入力信号の場合、閾値電圧付近または閾値を横切ると、出力が不安定になることがあります。シュミットトリガには、スイッチオン用の上限閾値とスイッチオフ用の下限閾値のXNUMXつの閾値があります。この場合、ノイズの多い入力がスイッチオン用の閾値を超えて再び上昇しても、上限閾値と下限閾値の差によって「保護領域」が形成され、デジタル出力は変化しません。このデバイスは、デバイストリガや正弦波-方形波コンバータとしてよく使用されます。

図 2: コンパレータとシュミット トリガの比較。

要件

シュミットトリガの構築と実装を始める前に、システムが以下の要件を満たしていることを確認してください。MATLABスクリプトからVHDLコードを生成するには、MATLABとHDL CoderおよびFixed-Point Converterが必要です。また、チュートリアルのパート2でSimulinkを使用してシステムを構築する場合は、Simulinkも必要です。注:Macユーザーは、HDL Coderが動作するためにXCodeもインストールされている必要があります。VHDLコードをコンパイルするには、Liquid Instruments Cloud Compileにアクセスできる必要があります。コンパイルされた計測器ビットストリームを実装するには、ファームウェアバージョン601以上を実行しているMoku:Pro、Moku:アプリ、および マルチインストゥルメントモード Moku:Pro で。

DSP設計

コンセプチュアルデザイン

シュミット トリガーには単一の入力と出力があります。アナログ入力信号は上限および下限のしきい値と比較されます。この例では、上限しきい値は正の入力範囲全体の 1/10 であり、下限しきい値は負の入力範囲全体の 1/10 です。入力信号が上限しきい値より高い場合、出力は 2^15-1 (出力が生成できる最大の 16 ビット符号付き整数) に設定されます。入力信号が下限しきい値よりも低い場合、出力は 0 に設定されます。または、これらの条件がいずれも満たされない場合は、前の状態のままになります。

浮動小数点 DSP 設計

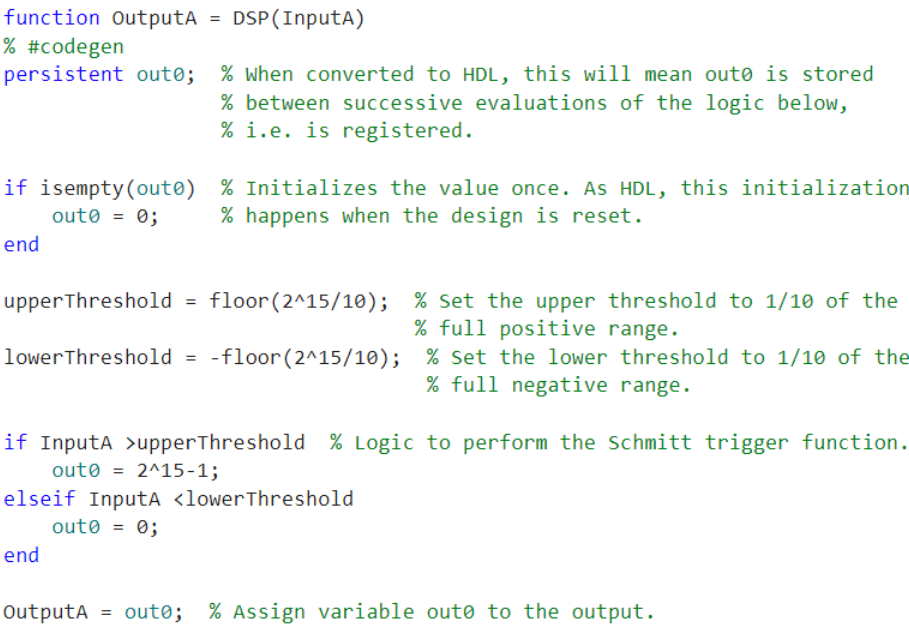

このセクションでは、永続変数と if-elseif ステートメントを使用して、上記の概念設計を MATLAB 関数に変換します。

シュミット トリガー DSP 関数では、1 つの入力チャンネル (InputA) と 1 つの出力チャンネル (OutputA) だけが必要になります。単一の入力と出力を備えた MATLAB 'DSP' を作成します。 DSP モジュールは関数形式で設計する必要があることに注意してください。

関数 出力A = DSP(入力A)

次に、関数に永続変数 out0 と論理演算の if-elseif ステートメントを設定します。

浮動小数点シミュレーション

シミュレーションと検証は、FPGA設計において非常に重要なステップです。デジタルシステムの応答を検証するためには、「テストベンチ」を構築するのが一般的です。テストベンチは、シミュレーション信号を入力してシステムの応答を観測するために使用されます。浮動小数点設計を固定小数点設計に変換するには、テストベンチが必要です。ネイティブ固定小数点設計の場合、テストベンチはオプションです。ただし、どのような設計でも必ずテストベンチシミュレーションを実行することを強くお勧めします。

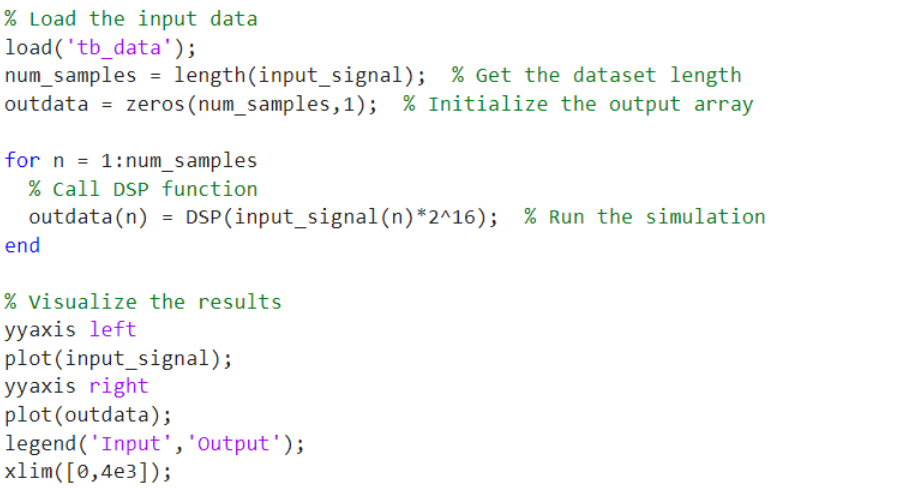

テストベンチの構築

MATLAB では、テストベンチは、さまざまな入力を使用してループ内で関数 (つまり、このチュートリアルでは DSP 関数) を呼び出す MATLAB スクリプトと考えることができます。このチュートリアルでは、浮動小数点設計、固定小数点設計、HDL 設計の 3 ラウンドのテストベンチ検証を実行します。最初のテストベンチは浮動小数点モデルを検証するもので、2 つ目は固定小数点変換後のシステム動作を検証するもので、最後は EDA ソフトウェアでの VHDL シミュレーションを通じて HDL モデルを検証するものです。

テストベンチの最初の 2 ラウンドは、MATLAB で、同じテストベンチ スクリプトを使用してシミュレートされた入力信号を使用して実行されます。シミュレートされた信号は、ダイナミック レンジと精度の点で実際の入力信号に非常に近いものである必要があります。これは、MATLAB の固定小数点ツールが固定小数点モデルに最適な精度を決定するのに役立ちます。

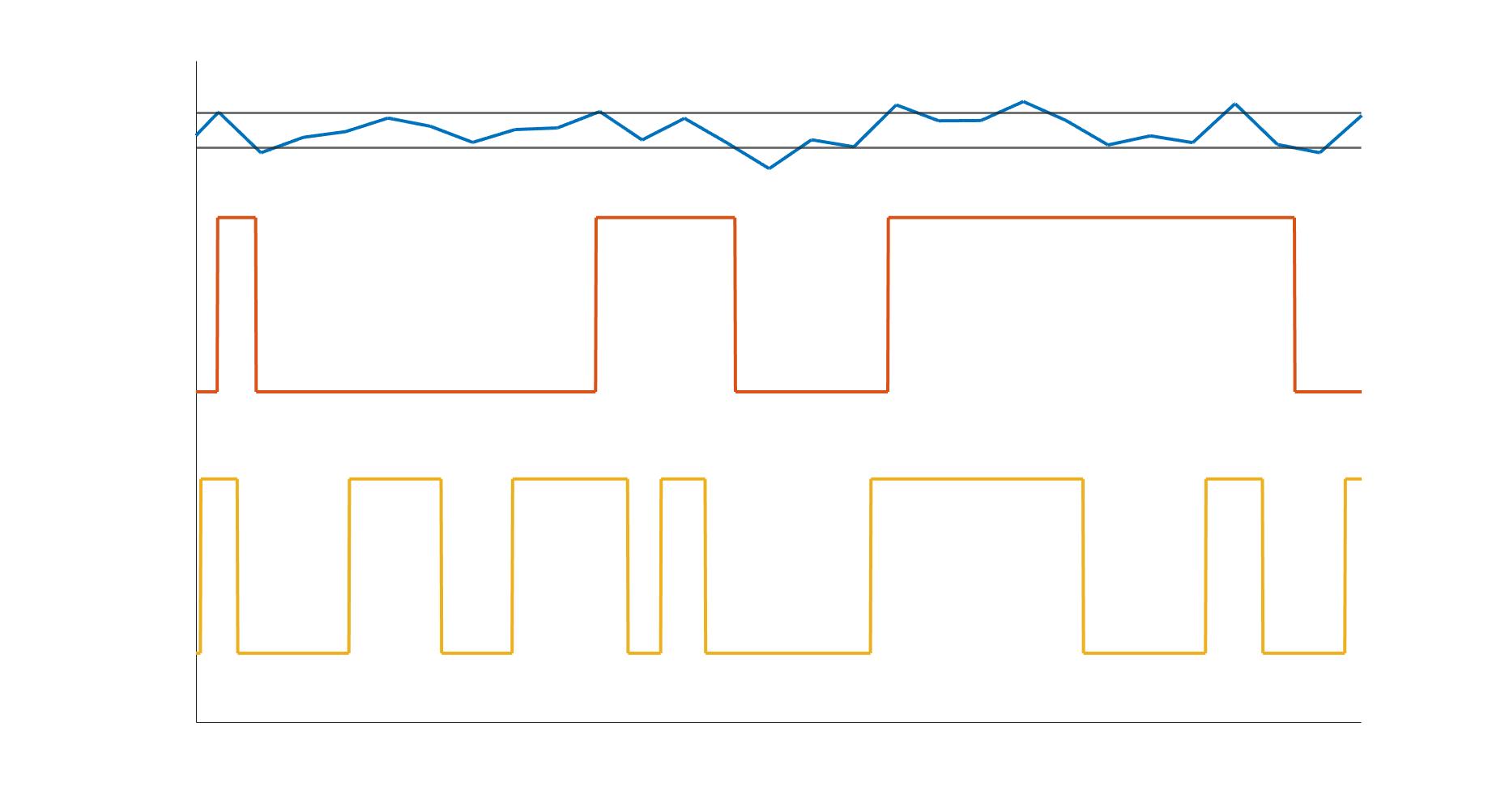

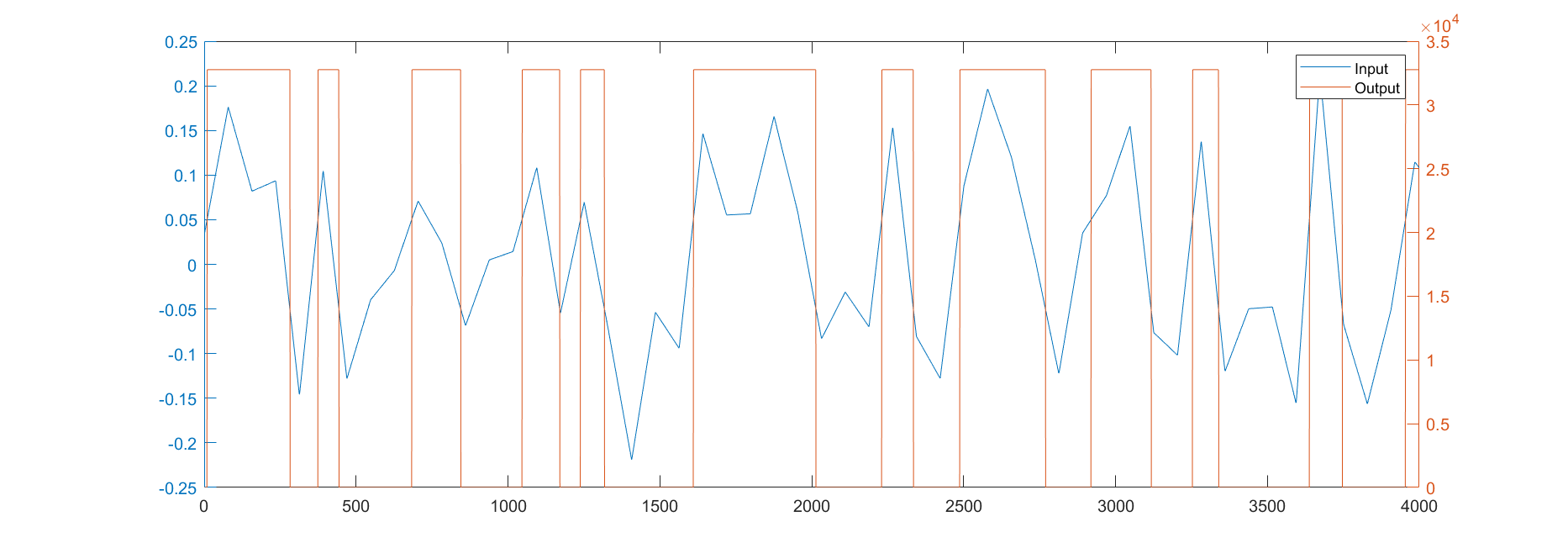

DSP関数テストベンチは、サンプルデータセットを入力信号として読み込むことで動作します。この信号は、チュートリアルのパート2で使用したSimulinkモデルと一致しています。DSP関数はforループ内で呼び出され、その出力は図3にプロットされています。出力から、DSP関数が設計しようとしていたシュミットトリガと一致していることが確認できます。これで、MATLAB HDL Coderを使用してHDLコードを生成する準備が整いました。

図 3: MATLAB シミュレーションの出力

HDLコード生成

MATLAB HDL Coder は、ワークフロー アドバイザーを使用して、固定小数点変換、HDL 生成、および HDL テストベンチ生成プロセスを含む完全な HDL コード生成プロセスをユーザーにガイドします。 DSP 関数を HDL コードに変換するこのプロセスを開始するには、まず MATLAB で HDL Coder アプリを起動し、新しいプロジェクトを作成します。あるいは、MATLAB のコマンド ウィンドウに「hdlcoder」と入力することもできます。

![図 4: HDL Coder アプリは [アプリ] タブにあり、新しい HDL Coder プロジェクトを作成できます。](https://liquidinstruments.com/wp-content/uploads/2021/10/Figure4.png)

図 4: HDL Coder アプリは [アプリ] タブにあり、新しい HDL Coder プロジェクトを作成できます。

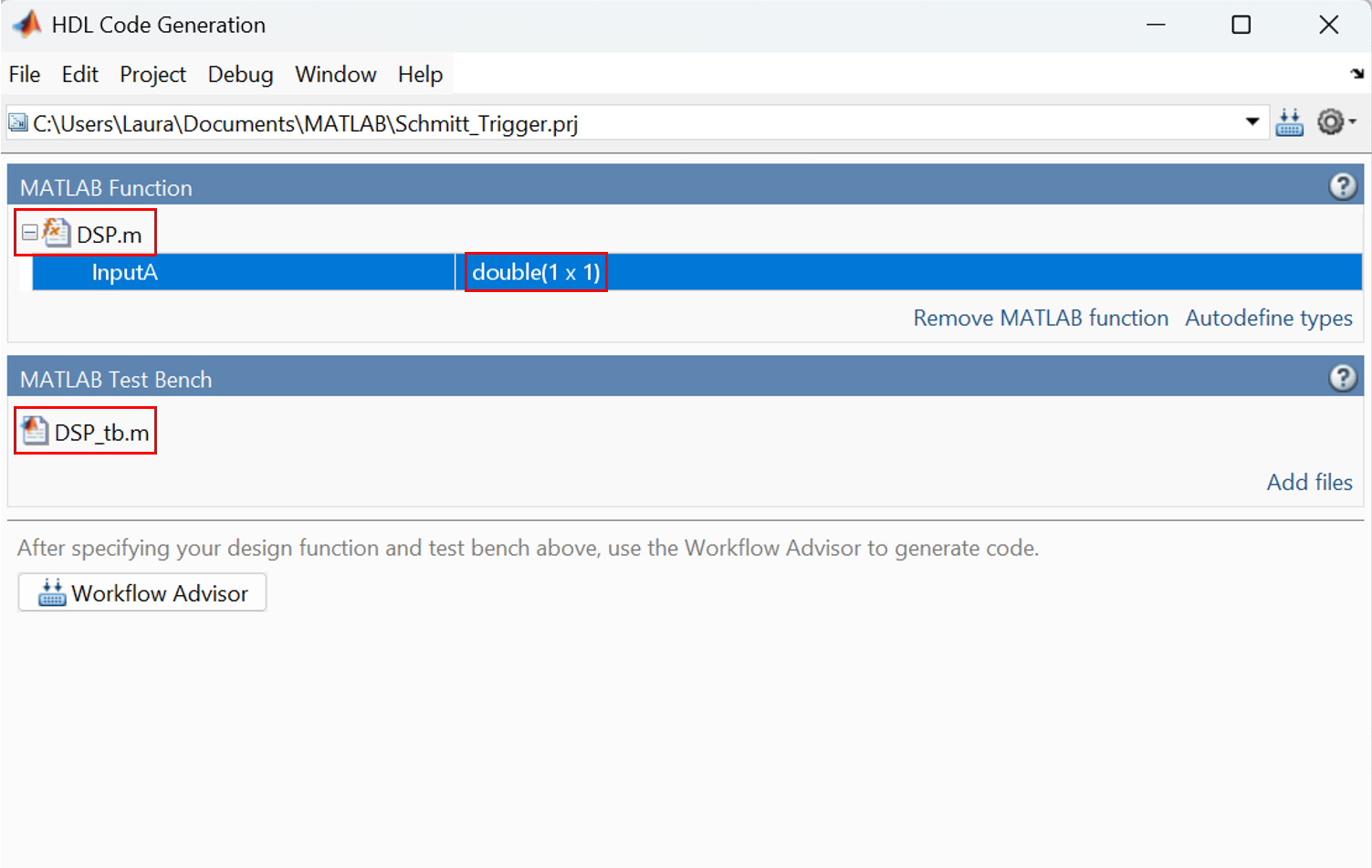

HDL コード生成ウィンドウが表示されたら、MATLAB 関数 (DSP) と対応するテストベンチを追加できます。ここで「タイプの自動定義」を使用して関数の入力変数タイプを定義することも、ワークフロー アドバイザでこれを完了することもできます。ほとんどの場合、入力変数は次のように定義できます。 、この時点ではモデルが浮動小数点であるためです。

図 5: DSP.m と DSP_tb.m は HDL 生成のソースとして使用されます。

これから開きます ワークフローアドバイザー シュミット トリガー HDL コードを生成します。

固定小数点変換

ソフトウェア モデルと FPGA モデルの主な違いの 1 つは、ソフトウェアの計算では通常浮動小数点数が使用されるのに対し、ほとんどの FPGA 計算では固定小数点数が必要であることです。 MATLAB のネイティブ形式は浮動小数点数です。したがって、この浮動小数点設計を HDL コード生成用の固定小数点モデルに変換する必要があります。

MathWorks の固定小数点ツールは、テストベンチの入力データ範囲に基づいて、浮動小数点モデルから固定小数点モデルへの自動変換を実行します。ユーザーは、必要に応じて、自動的に定義された範囲を手動でオーバーライドできます。 Moku Cloud Compile の場合、入力、出力、および制御信号タイプは、符号付き 16 ビット数値である Moku Cloud Compile インターフェイスと一致する必要があります。 MATLAB はこれを numerictype(1,16,0) として示します。ここで、「1」は信号を符号付き数値として指定し、「16」は語長を 16 ビットに指定し、「0」は XNUMX 進小数点スケーリングを指定しないことを意味します。

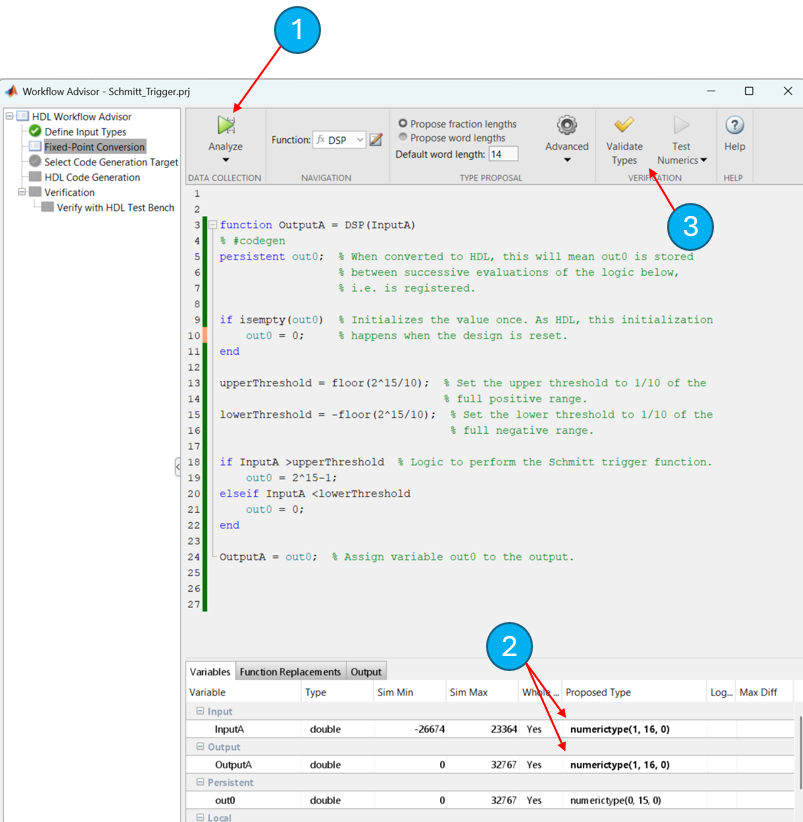

固定小数点変換を開始するには、まず [分析] ボタンをクリックし、HDL Coder がテストベンチ ファイルに基づいてデータ型と範囲を決定できるようにします。提案された型がハードウェア インターフェイス要件 (つまり、numerictype(1,16,0)) と一致しない場合は、変数の提案された型をクリックして numerictype(1,16,0) と入力することで、入力データ型と出力データ型を手動でオーバーライドします。 )。次に、「型の検証」をクリックしてデータ型を検証し、固定小数点モデルを生成します。

図 6: 1. テストベンチ入力信号を使用してデータ型を分析します。 2. 必要に応じて、データ型を手動でオーバーライドします。 3. 設計を検証し、固定小数点モデルを生成します。

固定小数点モデルの検証

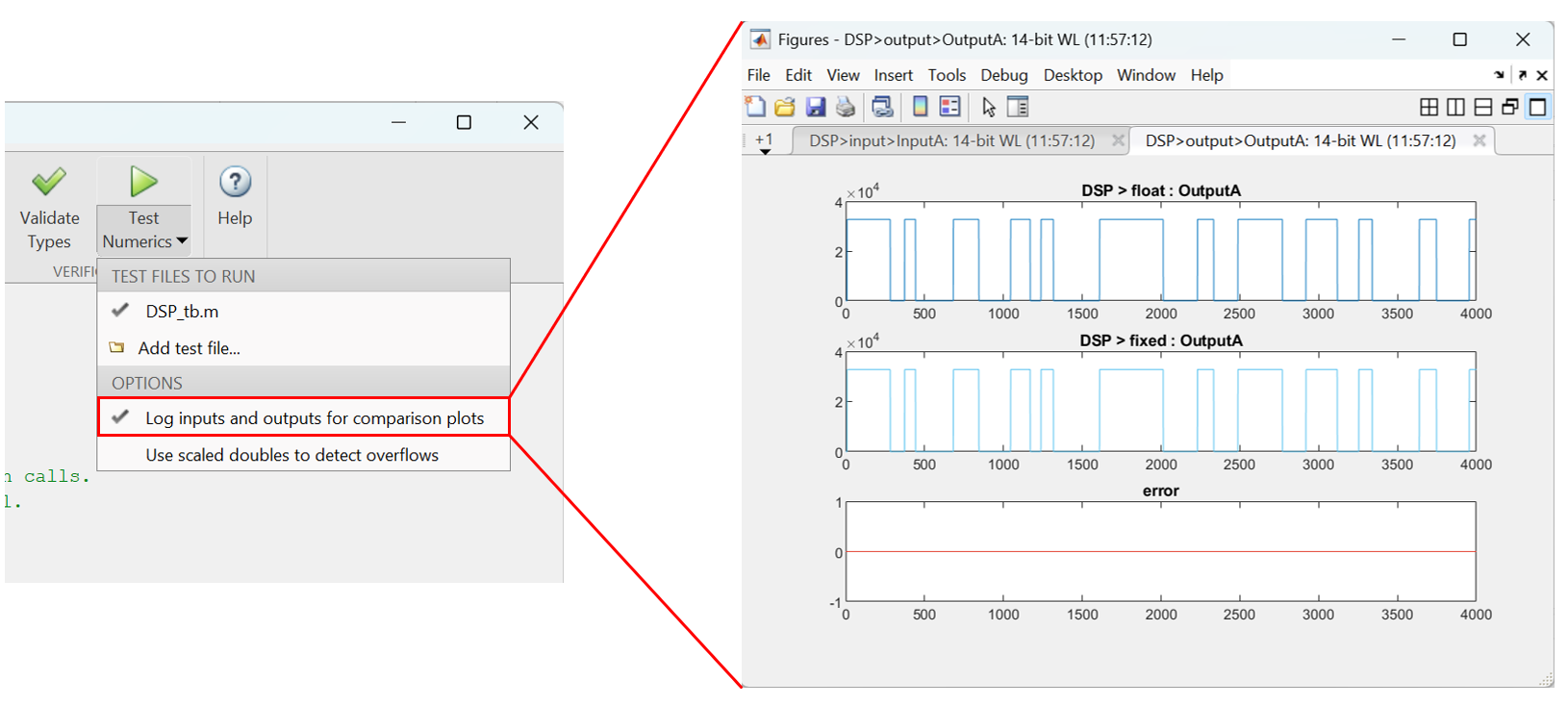

固定小数点モデルの変換後、別のシミュレーションを実行して、固定小数点モデルが期待どおりに動作することを確認し、精度の損失を評価する必要があります。固定小数点モデルの検証は、「Test Numerics」ボタンを通じて実行されます。必ず「比較プロットの入力と出力を記録する」を選択してください。これにより、浮動小数点モデルの変数を固定小数点モデルの同じ変数と比較するためのプロットが生成されます。

図 7: 浮動小数点モデルと固定小数点モデル間の変数 OutputA の比較

許容できない精度の損失が観察された場合は、変数の精度を上げてから、固定小数点変換を繰り返します。入力、出力、および制御信号の精度はハードウェア インターフェイスと一致する必要があることに注意してください。

固定小数点モデルがテストベンチでの検証に合格したら、シュミット トリガー モデルの VHDL コードの生成に進むことができます。

VHDLコード生成

メニューの「コード生成ターゲットの選択」に進み、「汎用 ASIC/FPGA」のままにします。

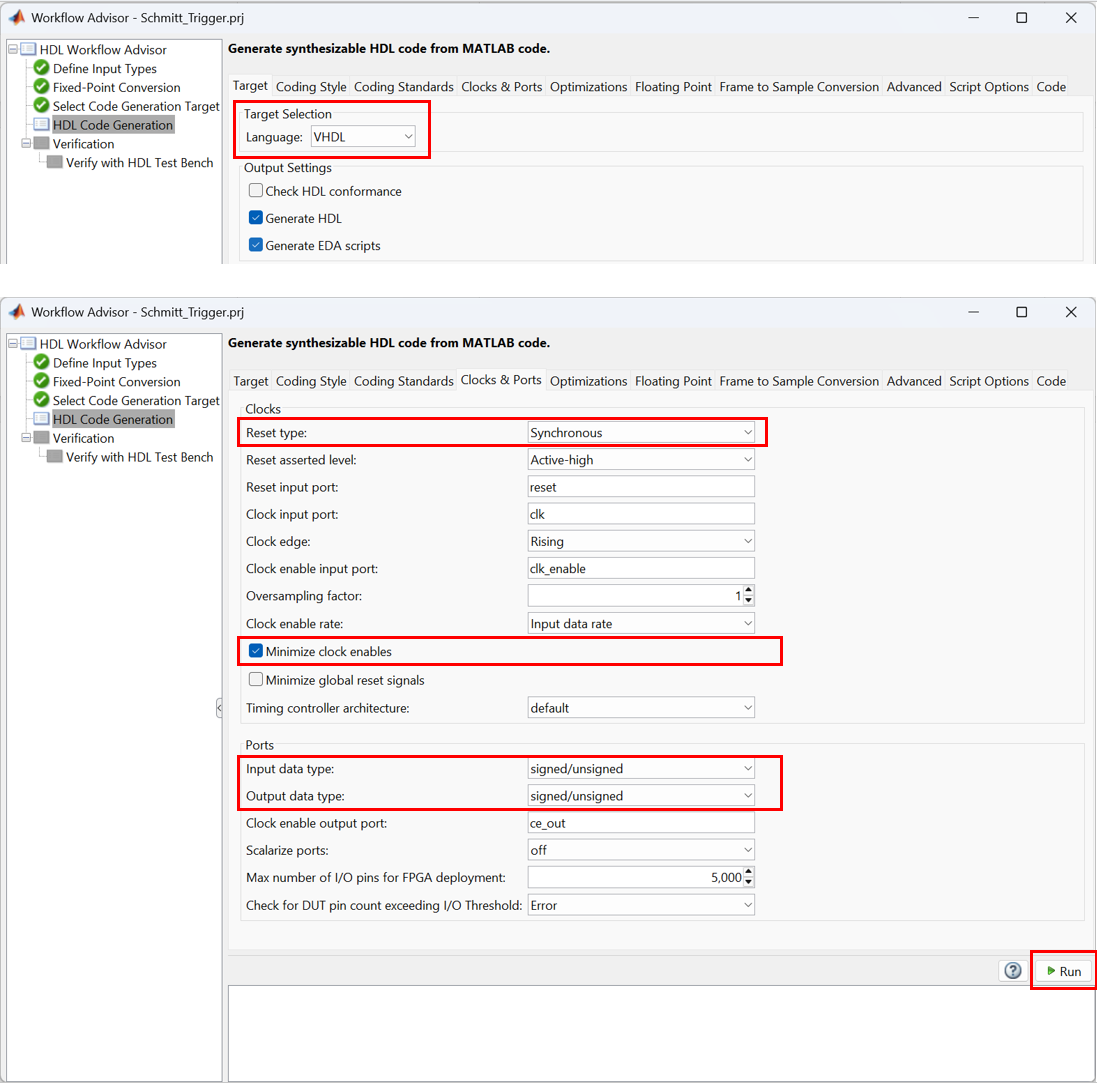

「HDL コード生成」ステップでは、「ターゲット」と「クロックとポート」を構成する必要があります。

- ターゲット:

- 作成セッションプロセスで 言語 〜へ VHDL

- クロックとポート:

- 作成セッションプロセスで リセットタイプ 〜へ 同期

- チェック クロックイネーブルを最小限に抑える

- 作成セッションプロセスで 入力データ型 〜へ 署名済み/署名なし

- 作成セッションプロセスで 出力データ型 〜へ 署名済み/署名なし

「実行」をクリックすると、システムの VHDL コードが下に表示されます。 …\ codegen\DSP\hdlsrc フォルダにコピーします。

図 8: VHDL へのターゲット言語を選択し、コード生成を実行する

サードパーティツールによるVHDLシミュレーション(オプション)

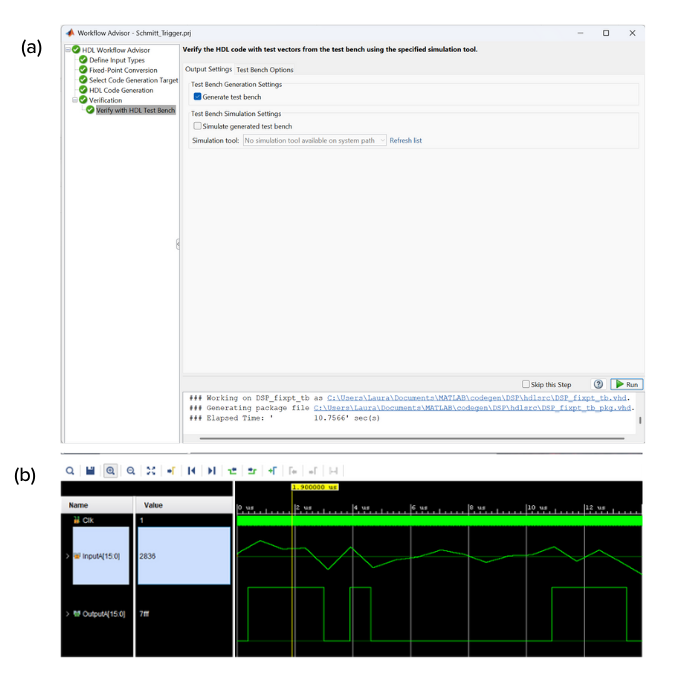

HDL Coder は、EDA ソフトウェアでシミュレーションを実行するための HDL テストベンチ ファイルを生成することもできます。サードパーティの HDL シミュレーターを使用してモデルを検証すると、設計に追加の保険が提供されます。この手順はオプションですが、複雑なシステムの場合は強くお勧めします。テストベンチ ファイルは、 ワークフローアドバイザー.

図 9: (a) HDL テストベンチ ファイルは HDL Coder で生成できます。 (b) Xilinx Vivado を使用した HDL レベルのシミュレーション。

コンパイルとデプロイメント

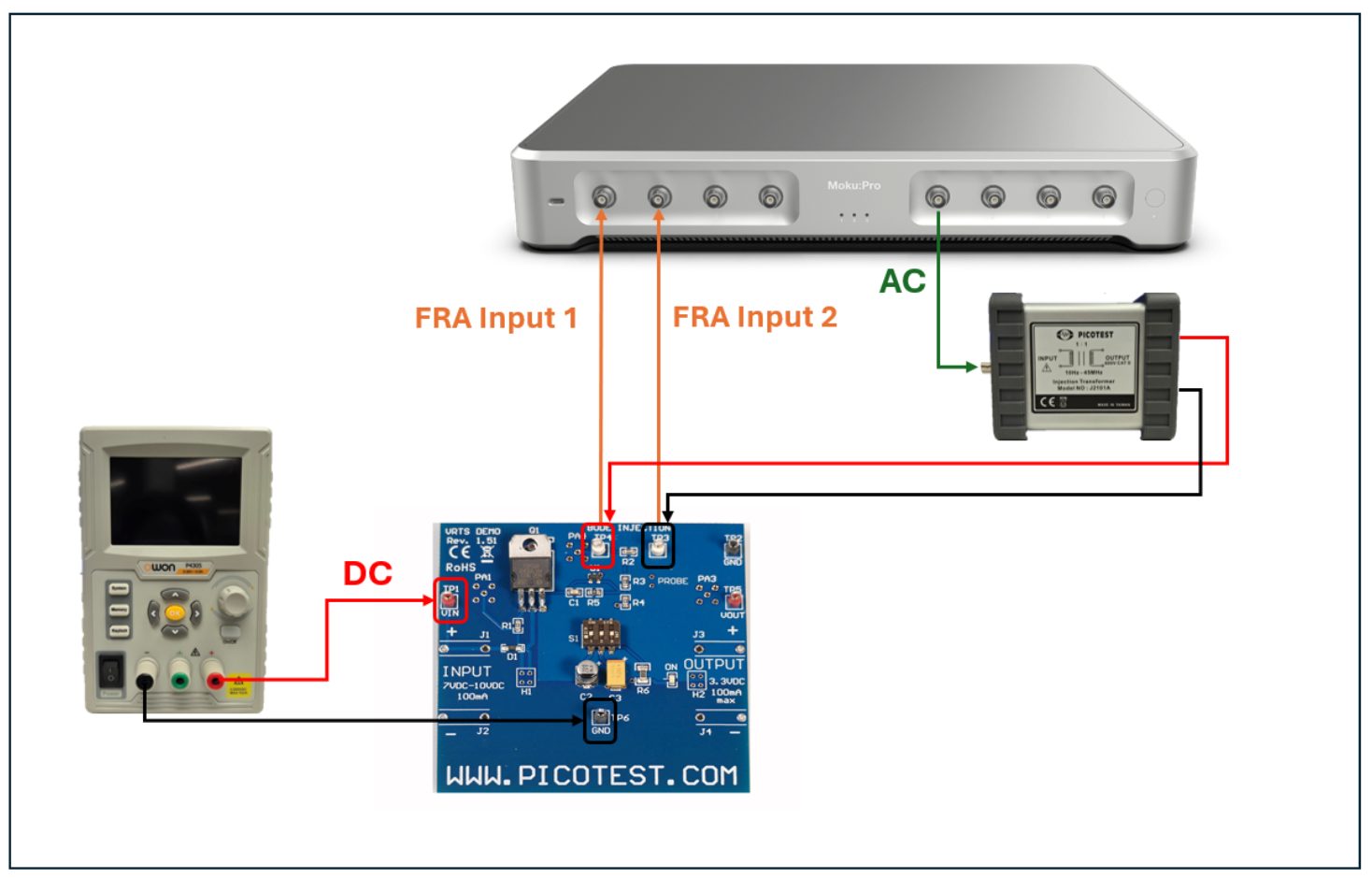

シュミット トリガーの VHDL コードが完成したので、Liquid Instruments の Moku Cloud Compile を使用して計測器をコンパイルし、Moku:Pro にデプロイする準備が整いました。

インストゥルメントラッパー

Moku Cloud Compileには標準の ラッパー カスタムインストゥルメントがMokuの他の部分と連携できるようにするために組み込まれています。標準のラッパーは、インストゥルメントの4つの入力チャンネルと出力チャンネルをすべて使用しますが、これは入力と出力がそれぞれ1つしかないシュミットトリガーの例とは一致しません。そのため、インストゥルメント用のカスタムラッパーを作成する必要があります。

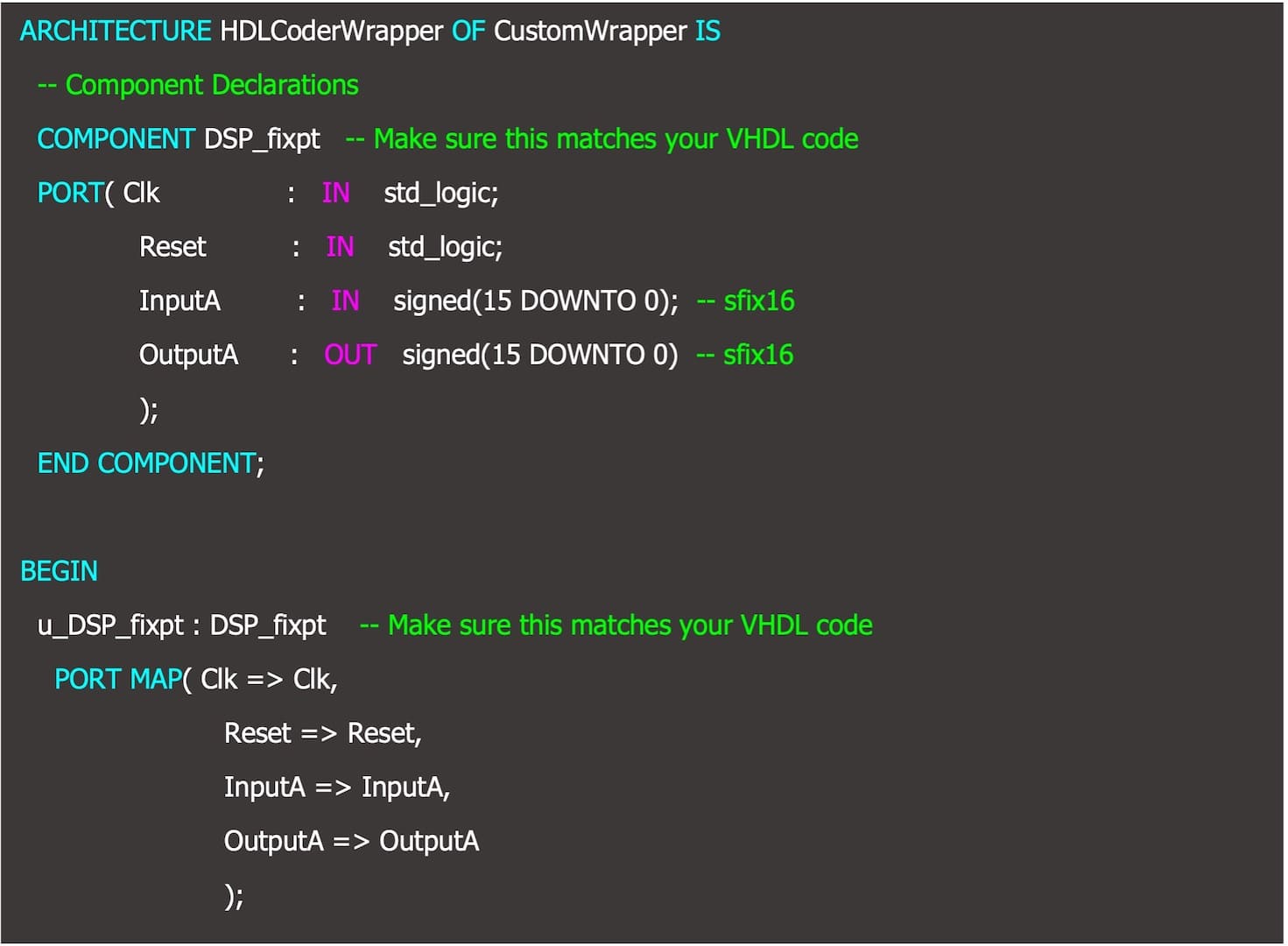

このチュートリアルには、MATLAB で生成された VHDL コードのラッパー テンプレートが提供されています。 3 つの異なるラッパー テンプレートが提供されています。1 つは MATLAB HDL Coder で生成された VHDL コード (つまり、このチュートリアル) 用に設計され、1 つは Simulink で生成された VHDL コード (つまり、このチュートリアルのパート II) 用に設計され、最後に 1 つはコード用です。が含まれています セアウト ポート。アプリケーションに適したラッパー テンプレートの選択に進む前に、VHDL コードのポート定義セクションを調べてください。

以下は、シュミット トリガー計測器のコンパイルに使用するカスタム ラッパーです。

計測器のコンパイルと展開

Moku Cloud Compile を使用して計測器のビットストリームを構築し、計測器を展開する方法の詳細な手順については、次のリンクを参照してください。 Moku Cloud Compile スタートガイド.

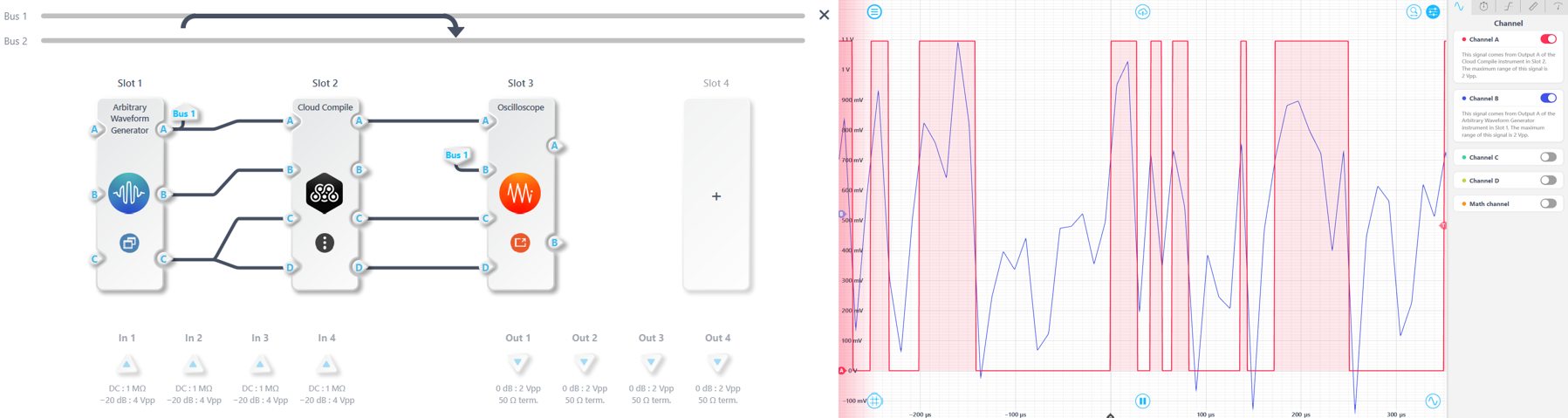

シュミットトリガをコンパイルするには、Liquid InstrumentsのMoku Cloud Compileで新しいプロジェクトを作成します。このプロジェクトで、シュミットトリガのVHDLコードであるDSP_fixpt.vhdのファイルを作成します。また、前のセクションで作成したカスタムラッパーのラッパーファイルも作成します。ターゲットデバイスとして4スロットのMoku:Proを選択し、プロジェクトをビルドします。ビットストリームがビルドされると、WebインターフェースとMoku:アプリを使用して、シュミットトリガをMoku:Proにデプロイできるようになります。

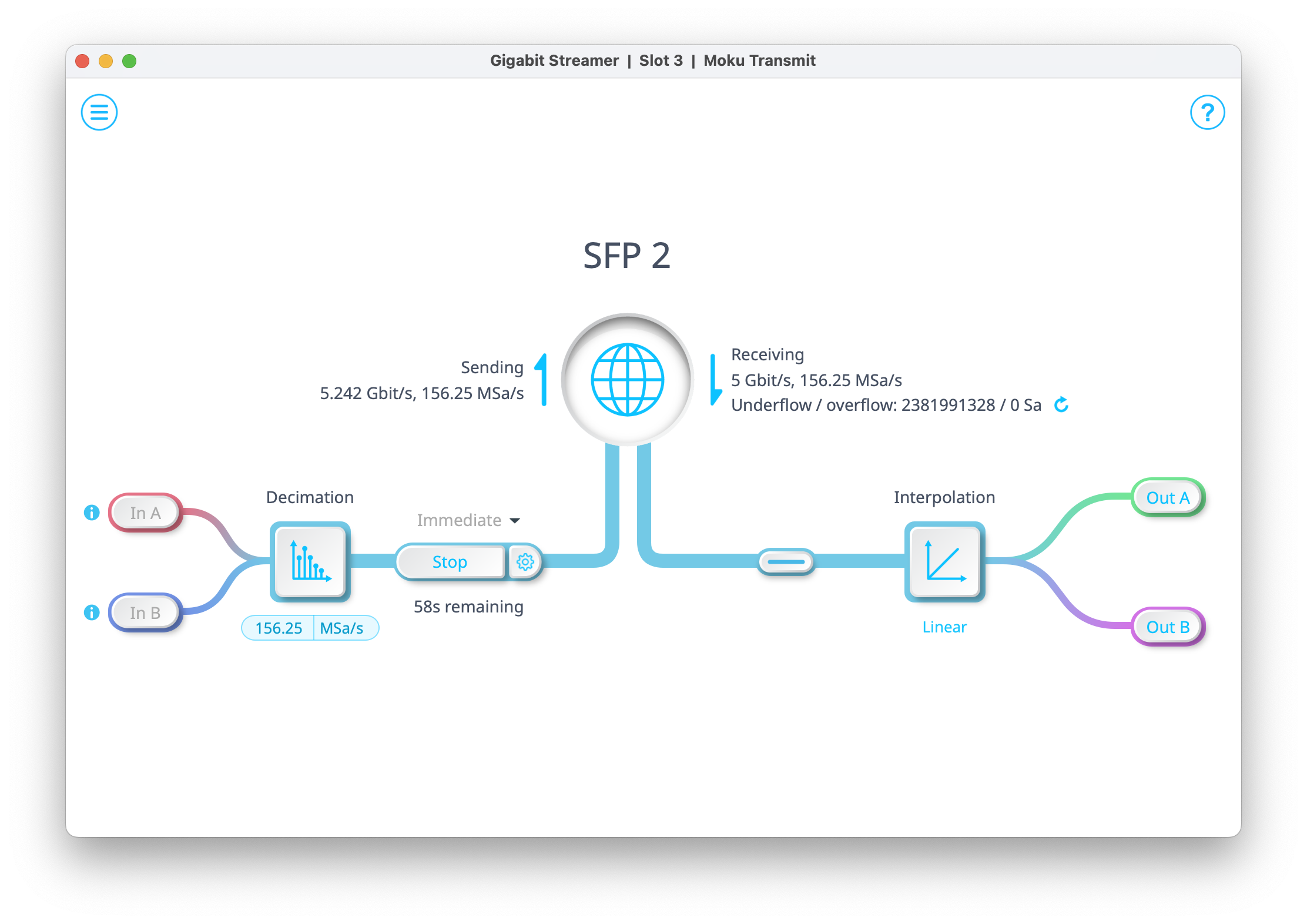

シュミットトリガが当初の概念設計どおりに機能していることを示すために、マルチ計測器モードで Moku: アプリを使用して、コンパイル済みの DSP をシステムに配置しました。スロット 1 には任意波形発生器を配置し、シュミットトリガへの入力信号としてテストベンチで使用したのと同じ信号を生成します。スロット 2 にはシュミットトリガを配置しました。スロット 3 にはオシロスコープを配置し、入力 1 にシュミットトリガからの出力、入力 2 に任意波形発生器からの信号出力を表示して信号を比較しました。信号が 110 mV を超えたときにシュミットトリガからの出力がハイに切り替わり、信号が -110 mV を下回るまでハイを維持していることがわかります。これにより、シュミットトリガが設計どおりに動作していることが確認できます。

図 10: (a) マルチ機器システム構成。 (b) シュミット トリガが設計どおりに機能していることを確認するオシロスコープ測定。

結論

このチュートリアルでは、MATLAB スクリプトを Moku プラットフォームで実装するためにコンパイルできる VHDL コードに変換する詳細なプロセスについて説明しました。このプロセスには、DSP 設計、浮動小数点シミュレーション、HDL 生成、DSP の導入と検証という 4 つのトップレベル プロセスが含まれます。このプロセスにより、HDL プログラミングを学習する必要がなくなり、ユーザーはすぐに独自のカスタム計測器の設計と作成に取り組むことができます。

コードの可用性

このプロジェクトのソースコードはダウンロードできます こちら.