アナログ信号は、遅延線を使用することで正確に遅延させることができます。時間的に量子化されたデジタルシステムでは、整数サンプルの遅延は簡単に実装できますが、分数遅延の実装はより困難です。幸いなことに、高度な FIRフィルタービルダー Liquid Instruments によって開発されたこのツールは、任意の信号に分数遅延を実装するための信頼性の高い強力なツールとして機能します。

FIR フィルタの動作は畳み込みの動作です。

ここで、n はサンプル インデックス、* は畳み込み演算子、y はフィルターの出力、x は入力、h はフィルターのインパルス応答です。畳み込みの便利なプロパティは次のとおりです。

遅延フィルタ出力を得るには、元の入力信号に遅延フィルタを適用するだけで済みます。たとえば、単純なユニティゲインのオールパスフィルタは次のように記述できます。

ここで、フィルタのインパルス応答はh[n]=δ[n]です。1サンプルの遅延を実装するには、次のフィルタを構築します。

遅延フィルタのインパルス応答([0]ではなく[1 1])が遅延出力につながることに注意してください。この方法では整数サンプルの遅延を簡単に生成できますが、分数遅延はまだ得られません(たとえばδ[0.5]を実装することはできません)。

部分的な遅延

フィルタの周波数応答は、そのインパルス応答のフーリエ変換です。信号の大きさを変えずに非整数遅延を実装するには、フーリエ変換がナイキスト周波数まで平坦でユニティゲインの周波数応答を持ち、その後、理想的には長方形のように、より高い周波数でゼロにロールオフする急峻なカットオフを持つフィルタ カーネルが必要です。このような関数の解析形式がわかっていれば、任意の遅延で評価できます。sinc 関数 (正弦基数) は長方形関数のフーリエ変換であることに注目すると、sinc 関数は非整数遅延を実装するための便利なプロトタイプ インパルス応答であることがわかります。sinc フィルタの引数に適切なオフセットを追加することで、その遅延を任意に制御できます。

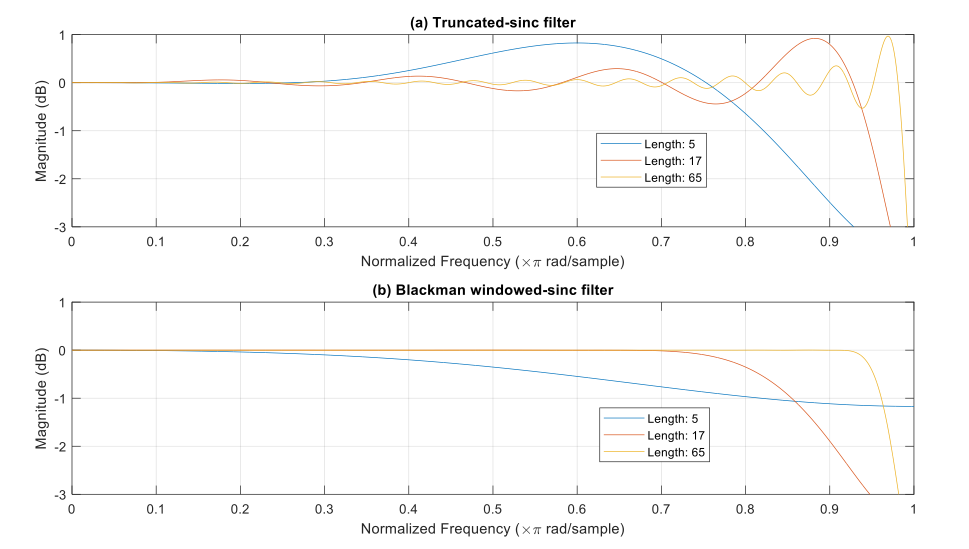

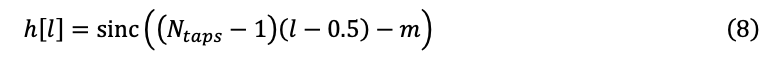

図 1: (a) 直接切り捨て sinc フィルタの周波数応答には大きなリップルが見られます。 (b) ブラックマン ウィンドウ sinc フィルタの周波数応答には最小のリップルが見られます。

窓付きシンク

理想的なブリックウォール周波数応答を実現するには、無限に長い sinc 関数が必要であり、したがってフィルター タップの数も無限に必要です。実際の FIR フィルターの長さは無限にはできないため、sinc フィルターを切り捨てる必要があります。フィルターを切り捨てることは、時間領域で長方形のウィンドウを乗算することと同じです。前述のように、これにより、周波数領域でブリックウォール応答と sinc 関数の畳み込みが行われ、フィルターの振幅応答が低下します。この誤差はフィルターが短いほど大きくなりますが、図 1(a) に示すように、1/(フィルター長) で徐々に改善されます。

切り捨てに関連するエラーは、エッジでの急激な不連続を避けるために sinc 関数をウィンドウ処理することで削減できます。帯域幅と通過帯域の平坦性の間でトレードオフを提供するウィンドウは多数存在します。図 1(b) では、オールパス遅延フィルタに望ましい比較的平坦な周波数応答を実現するために、ブラックマン ウィンドウ処理関数が適用されています。

方程式エディタ

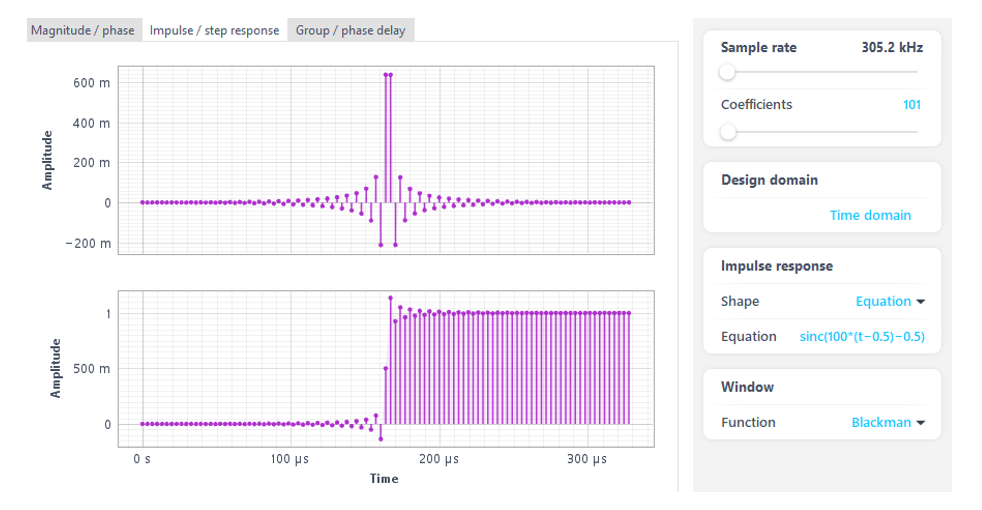

FIR フィルター ビルダー インストルメントは、時間領域と周波数領域の両方で指定できる、さまざまな構成可能なフィルターを提供します。さらに、カスタム インパルス応答をアップロードしたり、組み込みの方程式エディターを使用して定義したりすることもできます。sinc 関数は定義済みオプションとして含まれていますが、ここでは教育演習として、方程式エディターを使用して実現する方法を示します。

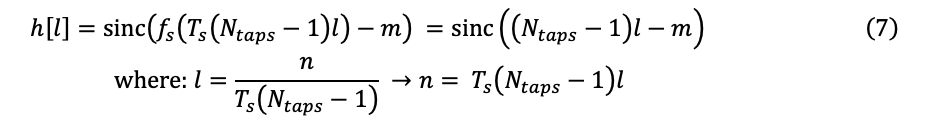

数学的には、帯域制限されたユニティゲインを実現するシンクフィルタは、 ナイキスト周波数 範囲は次のように表すことができます。

![]()

ここで、mはサンプリング周期Tの単位での所望の遅延である。s= 1/fs

シンクフィルタの時間長はTs (Nタップ-1)。ただし、FIRフィルタビルダでは、方程式エディタの公称時間ベースは1です。FIRフィルタビルダ内でsincフィルタの形状を維持するには、式6のnをTの係数で減らす必要があります。s (Nタップ-1)。したがって、FIR フィルタ ビルダーのフィルタ方程式は次のようになります。

重要な考慮事項の7つは、式XNUMXのsinc関数が区間 ![]() sincフィルタの中心をFIRフィルタウィンドウの中心に配置し、因果関係を維持する(定義範囲を[0,Nタップ-1] )、この式はさらに次のように改良することができます。

sincフィルタの中心をFIRフィルタウィンドウの中心に配置し、因果関係を維持する(定義範囲を[0,Nタップ-1] )、この式はさらに次のように改良することができます。

図 2: 50 サンプリング期間の遅延に対する FIR フィルタ チャネル A の構成。

図 3: 50.5 サンプリング周期の遅延の FIR フィルタ チャネル B 構成。

例:

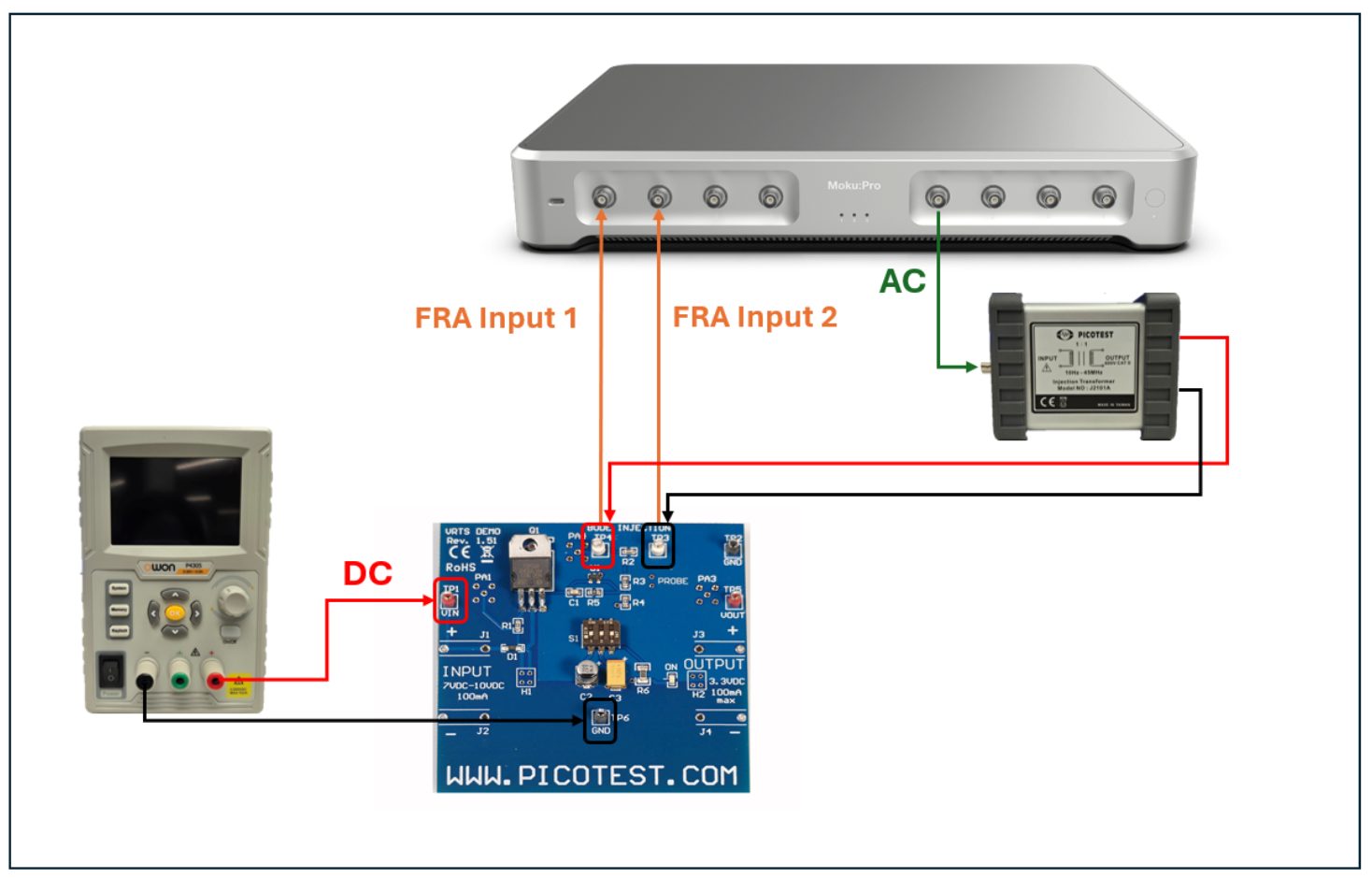

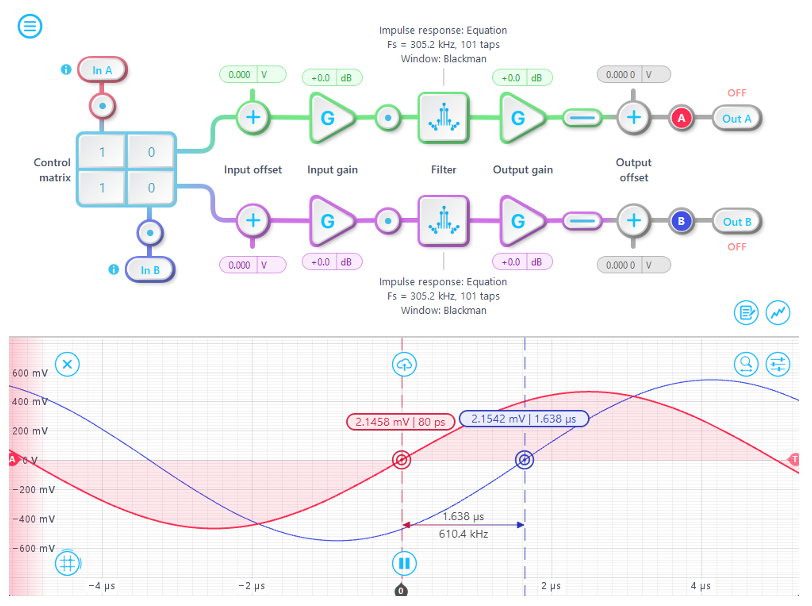

図 2 と図 3 は、FIR フィルタ ビルダーの 50 つのチャネルの構成を示しています。チャネル A では、50 サンプリング周期の遅延が提供され、フィルタ係数は中央に正確に位置する単一のピークを示します。このピークは基本的にデルタ関数 δ[n-50.5] を表します。チャネル B は、デジタル化された sinc 関数を正確に表示します。sinc 関数の中心は 4 つの FIR タップの間に位置しているため、単一のピーク値は存在しません。このパスは、入力信号を 1 サンプル遅延します。図 2 は、XNUMX つのパス間の XNUMX/XNUMX サンプリング周期の遅延が正確に実現されていることを示しています。

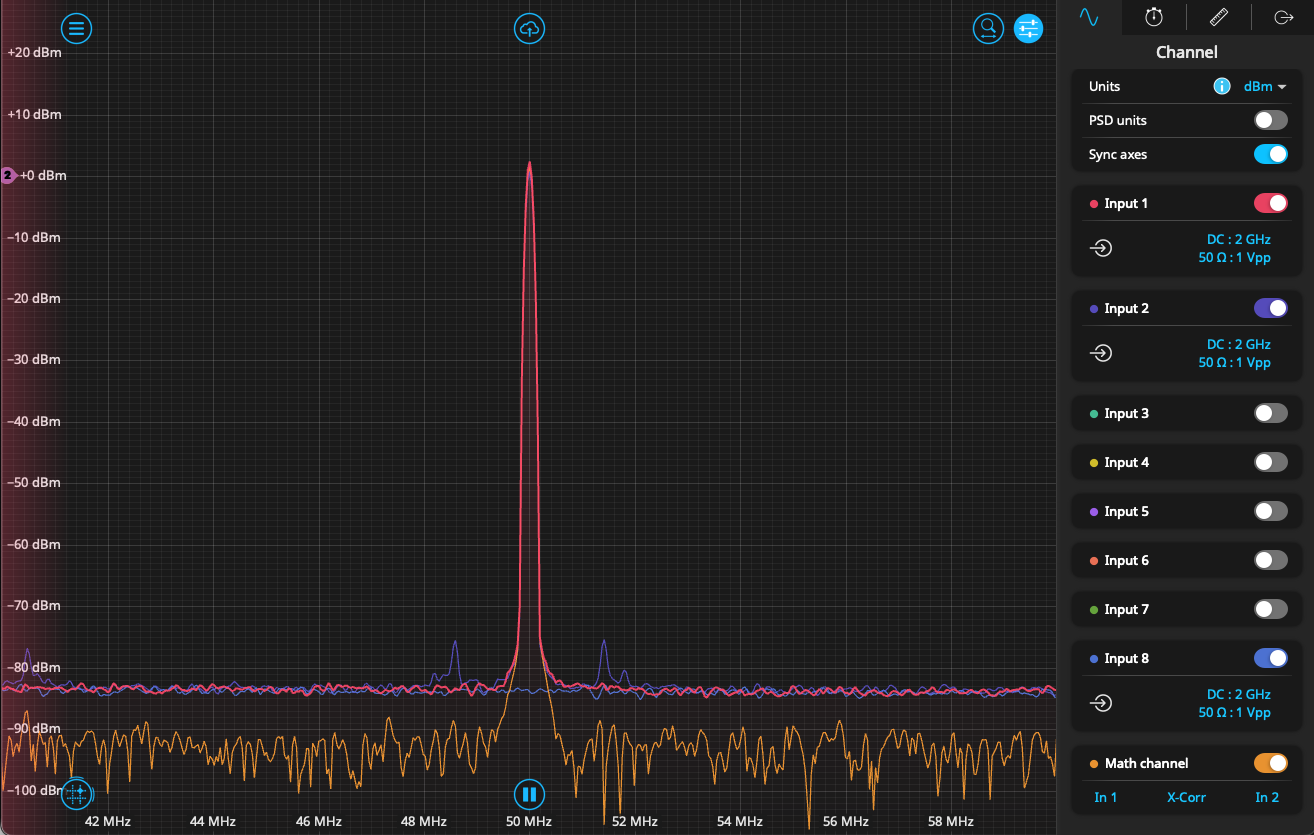

図 4: チャネル B (青) では、チャネル A (赤) と比較して 1/2 サンプリング周期の遅延が見られます。

結論

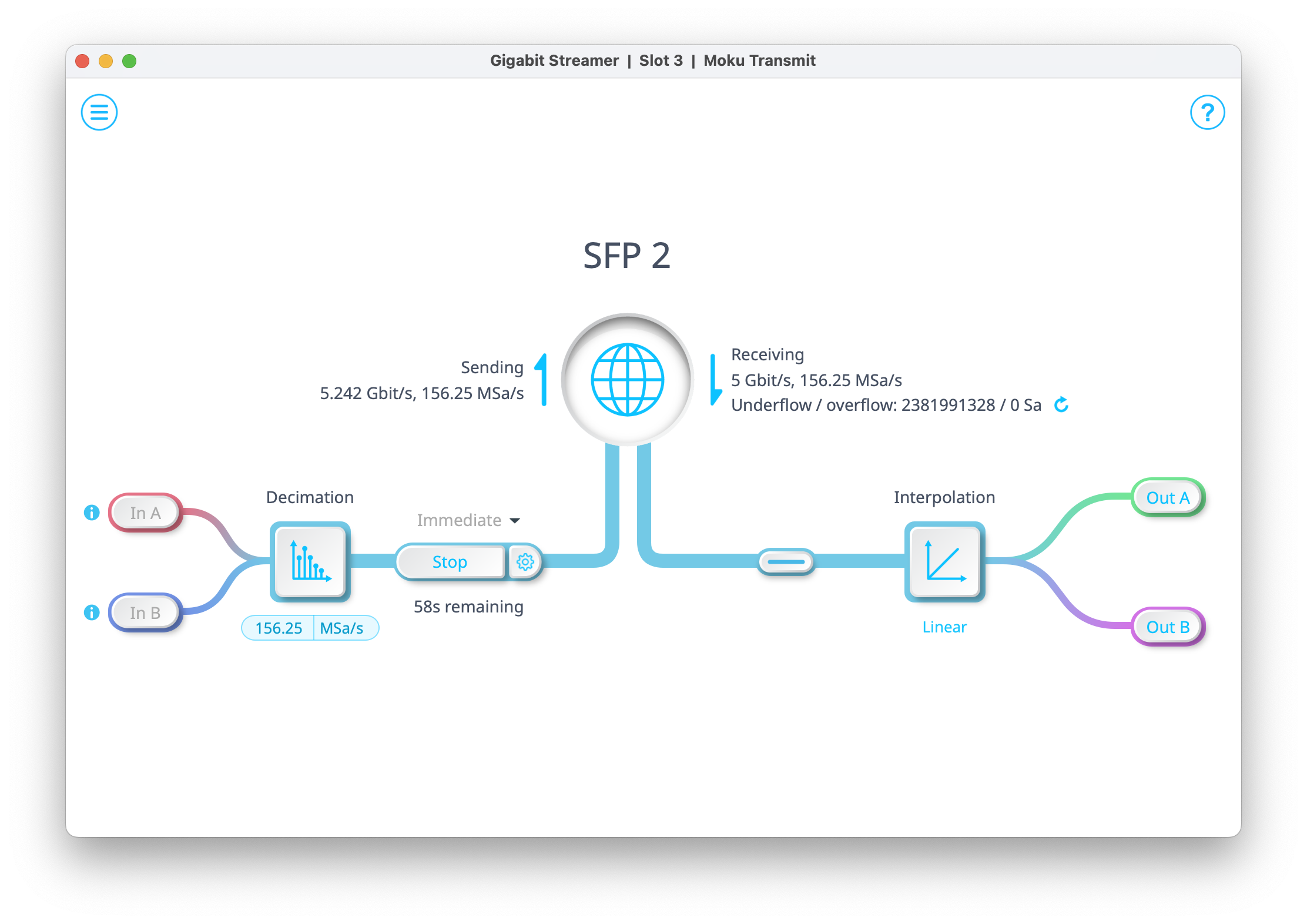

信号の正確な調整と遅延の補正は、さまざまな制御および信号伝送アプリケーションで重要です。堅牢なFIRフィルタビルダーを使用すると、信号ラインの遅延を非常に正確に制御できます。さらに、FIRフィルタビルダーは他の機器やカスタムとシームレスに組み合わせることができます。 Mokuクラウドコンパイル コード内 マルチインストゥルメントモード 複雑な統合テスト環境でも正確で精度の高い結果を保証します。

分数遅延生成の詳細については、 アプリケーションノート.